C2S Programme: Scaling Indigenous Chip Design Skills, Infrastructure, and Start-up Innovation

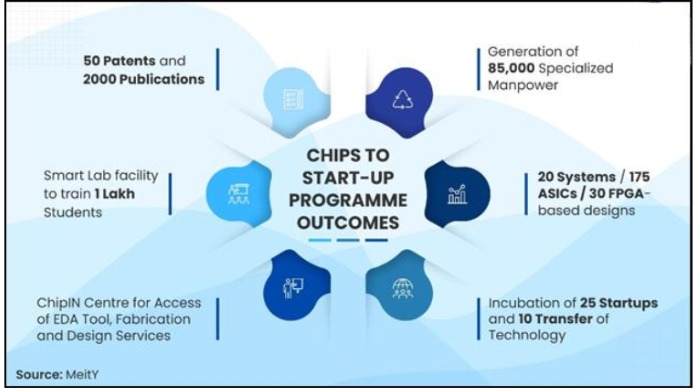

1. Chips to Start-up Programme is a national capacity-building initiative launched in 2022, with ₹250 crore over five years, expanding chip design education, fabrication exposure, and innovation across institutions.

2. It targets creation of 85,000 industry-ready professionals across UG, PG, and PhD levels nationwide, including 200 PhDs, 7,000 VLSI M.Tech, 8,800 allied M.Tech, and 69,000 B.Tech trainees overall.

3. Nearly one lakh individuals enrolled for chip design training, and about 67,000 have been trained so far, addressing global semiconductor talent shortages and strengthening domestic skill pipelines rapidly.

4. Programme ecosystem spans about 400 organisations: 305 academic institutions under C2S and 95 startups under a complementary incentive scheme, widening participation beyond elite campuses nationwide into innovation networks.

5. It aims to catalyse 25 start-ups and enable 10 technology transfers, while expanding SMART lab access, training one lakh students, generating 50 patents, and supporting 2,000 research publications.

6. Hands-on learning is delivered through industry-led training, mentorship, and access to advanced EDA software, foundry interfaces, fabrication facilities, and testing resources for designing, building, and validating chips securely.

7. Participating institutions pursue prototypes of ASICs, Systems-on-Chip, and reusable IP cores, bridging curriculum learning with full workflows from architecture and verification to tape-out, fabrication, testing, and post-silicon evaluation.

| Coordinating Organization | Mode | Area | |

| 100+ Participating Academic Institutions

(Beneficiaries of project funds, EDA Tools & trainings) |

|

End-to-end exposure to chip design, fabrication, and testing through R&D projects | |

| 200+ Other Organizations

(Beneficiaries of EDA Tools & trainings) |

Instruction as part of curriculum, Short-term courses, labs, and student projects. | General chip design flows using advanced EDA tools. | |

| ChipIN Centre, C-DAC Bangalore

(Serving 300+ institutions) |

Regular training sessions with industry partners. Facilities include: | Specialized design areas using advance tools.

|

|

| EDA tools | Synopsys, Cadence, IBM, Siemens EDA, Ansys, Keysight Technologies, Silvaco, AMD, Renesas | ||

| Foundry access | SCL, IMEC, MUSE Semiconductors | ||

| Chip design flow | ChipIN Centre, NIELIT | ||

| SMART Lab, NIELIT Calicut (Pan-India institutions) | Identified short-term and certification courses. | General chip design flows using centralized hardware resources. | |

8. ChipIN Centre at C-DAC Bengaluru functions as a national shared design infrastructure hub, supporting 300+ institutions with tools, compute, IP libraries, mentoring, and structured design onboarding services nationwide.

9. ChipIN Centre conducted six shared wafer runs and 265+ training sessions, while addressing 4,855 support requests, demonstrating sustained technical assistance and operational scale for academic chip programmes nationwide.

10. Designs are collected, verified for fabrication readiness, iterated with feedback, aggregated onto shared wafers, and sent every three months to SCL Mohali for fabrication using 180 nm technology.

11. SCL Mohali enabled large-scale hands-on design: 122 submissions from 46 institutions, with 56 student-designed chips successfully fabricated, packaged, tested, and delivered back for real silicon validation for learning.

12. Shared national EDA infrastructure recorded over 175 lakh hours of tool usage by users across 400 organisations, indicating intensive practical engagement with professional-grade electronic design automation platforms nationwide.

13. Institutions filed 75+ patents and are developing 500+ IP cores, ASICs, and SoC designs, with applications spanning defence, telecom, automotive, consumer electronics, and industrial systems integration nationwide today.

14. FPGA boards were distributed through centralised and distributed models to support prototyping and design validation, complemented by high-performance computing access via the PARAM Utkarsh supercomputer resources nationally effectively.

15. Coordinated institutional framework links policy direction, funding, and oversight with infrastructure operators and fabrication facilities, ensuring equitable access, stronger academia–industry collaboration, and a steady pipeline of chip designers.

Must-Know Terms :

1.Chips to Start-up (C2S) Programme: Chips to Start-up is a MeitY capacity-building umbrella launched in 2022 to democratise chip design. It funds training, curriculum integration, labs, and R&D projects, linking students with industry mentors and national infrastructure. Its targets include 85,000 professionals, start-up incubation, patents, technology transfers, and silicon validation, strengthening self-reliant design capability across diverse institutions nationwide, including smaller colleges too, for long-term resilience.

2.ChipIN Centre: ChipIN Centre, operated by C-DAC Bengaluru, provides shared semiconductor design infrastructure for hundreds of institutions. It offers commercial EDA tool access, compute, IP libraries, onboarding, and mentoring. It aggregates student designs, verifies fabrication readiness, and organises periodic multi-project wafer submissions. It also runs frequent training and resolves technical support tickets, accelerating hands-on learning and reproducible design outcomes consistently, nationwide regularly.

3.Shared Wafer Run: A shared wafer run pools multiple validated chip layouts from different teams onto one wafer, reducing fabrication costs per participant. ChipIN collects designs, checks rule compliance, coordinates iterations, and tapes out combined masks. SCL fabricates the wafer, then packages and returns individual dies. This approach enables students to experience real fabrication cycles, post-silicon testing, and design improvement loops quickly, repeatedly.

4.Electronic Design Automation (EDA) Tools: EDA tools are professional software suites used to design, simulate, verify, and layout integrated circuits. They support steps like RTL coding, synthesis, timing analysis, place-and-route, signoff checks, and verification. Access to commercial platforms through shared national infrastructure lets learners practice industry workflows, reduce errors before fabrication, and build reusable design blocks that meet foundry requirements reliably, at scale, and compliance.

5.Semi-Conductor Laboratory (SCL) Mohali and 180 nm: SCL Mohali provides fabrication and packaging support for student designs under the programme. Designs are manufactured using an established 180 nanometre process, suitable for training, prototyping, and many control-oriented applications. After fabrication, chips are packaged and delivered back to teams for validation. This closes the loop from design to silicon, making learning evidence-based and measurable for institutions nationwide, and confidence.

6.FPGA and PARAM Utkarsh Support: Field Programmable Gate Arrays let designers prototype digital logic and verify functionality before committing to fabrication, cutting risk and iteration time. The programme supplies FPGA boards through central and distributed modes for labs and projects. High-performance computing via the PARAM Utkarsh supercomputer supports demanding EDA workloads and simulations. Together, they enable scalable learning, faster verification, and more robust tape-outs effectively.

Key Takeaways

- Over 1 lakh individuals have enrolled in chip design training, with approximately 67,000 trained so far.

- The ChipIN Centre conducted 6 shared wafer runs and 265+ training sessions in collaboration with industry partners.

- The Semi-Conductor Laboratory (SCL) enabled hands-on chip design at scale, with 122 submissions from 46 institutions, including 56 student-designed chips successfully fabricated, packaged, and delivered.

- Participating institutions have filed 75+ patents and are developing 500+ IP cores, ASICs and SoC designs.

MCQ

1. With reference to the Chips to Start-up programme, consider the following statements:

1) It was launched in 2022 with an outlay of ₹250 crore over five years.

2) It targets development of 85,000 industry-ready professionals.

3) It is limited to a small set of premier institutions only.

a) 1 and 2 only

b) 2 and 3 only

c) 1 and 3 only

d) 1, 2 and 3

2. The ChipIN Centre is best described as:

a) A fabrication-only unit that manufactures chips without design support

b) A national shared design enablement hub providing tools, compute, IP, and mentoring

c) A funding agency that disburses scholarships for overseas VLSI study

d) A standards body that certifies EDA tools for global markets

3. Under the programme workflow, designs are typically sent for fabrication:

a) Weekly

b) Monthly

c) Every three months

d) Once in five years

4. With reference to shared wafer runs, consider the following:

1) Multiple validated designs are combined onto a single wafer.

2) It reduces per-participant fabrication costs.

3) It prevents post-silicon testing by restricting chip delivery.

a) 1 and 2 only

b) 2 and 3 only

c) 1 and 3 only

d) 1, 2 and 3

5. Which one of the following is stated as the fabrication technology used for student designs at SCL Mohali?

a) 7 nm

b) 28 nm

c) 65 nm

d) 180 nm

6. Consider the following pairs:

1) Enrolled for training — About 1 lakh

2) Trained so far — About 67,000

3) Tool usage — Over 175 lakh hours

Which of the pairs given above are correctly matched?

a) 1 only

b) 1 and 2 only

c) 2 and 3 only

d) 1, 2 and 3

7. Match List-I with List-II:

List-I: (A) ASIC (B) SoC (C) IP Core

List-II: (1) Reusable design block (2) Application-specific integrated circuit (3) System-level integrated chip

a) A-2, B-3, C-1

b) A-3, B-2, C-1

c) A-1, B-3, C-2

d) A-2, B-1, C-3

8. Assertion (A): The programme strengthens practical learning by enabling silicon validation.

Reason (R): Student designs are fabricated, packaged, and delivered back for testing and evaluation.

a) Both A and R are true, and R is the correct explanation of A

b) Both A and R are true, but R is not the correct explanation of A

c) A is true, but R is false

d) A is false, but R is true

9. With reference to programme outcomes, which of the following is stated?

a) 122 submissions came from 122 institutions, and 122 chips were delivered

b) 122 submissions came from 46 institutions, and 56 chips were delivered

c) 56 submissions came from 122 institutions, and 46 chips were delivered

d) 46 submissions came from 56 institutions, and 122 chips were delivered

10. The stated number of shared wafer runs conducted by the ChipIN Centre is:

a) 3

b) 6

c) 12

d) 24

11. The stated number of industry-led training sessions conducted is:

a) 65+

b) 122+

c) 265+

d) 500+

12. Which of the following best captures the role of EDA tools in the programme?

a) Replacing fabrication with software-only certification

b) Enabling design, verification, and layout workflows before fabrication

c) Limiting design choices to manual drafting on paper

d) Preventing aggregation of designs onto shared wafers

13. Consider the following statements about ecosystem coverage:

1) About 305 academic institutions participate under the programme.

2) About 95 startups participate under a complementary incentive scheme.

a) 1 only

b) 2 only

c) Both 1 and 2

d) Neither 1 nor 2

14. Assertion (A): FPGA boards reduce development risk for chip fabrication.

Reason (R): They allow prototyping and design validation before committing to fabrication runs.

a) Both A and R are true, and R is the correct explanation of A

b) Both A and R are true, but R is not the correct explanation of A

c) A is true, but R is false

d) A is false, but R is true

15. Which one of the following is stated as supporting high-performance computing for demanding design workloads?

a) Bharat Mandapam cluster

b) PARAM Utkarsh supercomputer

c) INSAT ground station

d) National optical fibre backbone

0 comment